“Precision Low-Dropout Regulators” Online Course (2025)

Interview with Prof. Yan Lu (Tsinghua University)

Preview – “Precision Low-Dropout Regulators” Online Course (2025)

Sample Lecture – “Precision Low-Dropout Regulators” Online Course (2025)

HW #3 – “Precision Low-Dropout Regulators” Online Course (2025)

Noise-sensitive analog front-ends in System-on-Chip (SoC) and mixed-signal designs rely on Low-Dropout Regulators (LDOs) to deliver high power supply rejection (PSR) and fast transient response which are critical for maintaining on-chip power integrity. As essential building blocks in modern SoCs, LDOs must balance several trade-offs: power efficiency versus speed, dropout voltage versus PSR, and precision versus quiescent current and loop bandwidth. The move toward capacitor-less designs, which frees valuable I/O pins, introduces further design challenges, particularly in achieving high PSR and minimizing transient voltage undershoot.

This short-course covers the fundamental principles of LDO design, practical implementation techniques, and in-depth control loop analysis. It explores fully integrated, capacitor-less LDO topologies, offering real-world case studies of analog, digital, and distributed LDO architectures suited for large-scale SoC applications in nanoscale CMOS technologies.

The course begins with an intuitive introduction to key design concepts, including power transistor selection, gate-drive buffer design, dynamic biasing techniques, and PSR design considerations. Existing LDO architectures are reviewed through the framework of classical PID control theory, offering a simplified approach to understanding complex multi-loop designs.

Next, we’ll examine practical techniques and LDO design variants. Topics include feedforward ripple cancellation, LDOs with cascode power transistors, digitally controlled and synthesizable LDOs, and distributed LDO architectures designed for robust operation in large-scale systems.

In the final section, two detailed design and simulation projects are presented, one focused on achieving high bandwidth and the other on maximizing PSR. The participants will have the opportunity to develop and compare their own design solutions based on project parameters.

Each lecture is complemented by optional homework assignments that encourage participants to apply and extend their learning beyond the classroom. These exercises may involve SPICE simulations or analytical circuit design problems, offering practical experience that reinforces key concepts.

This course is aimed at analog, power management, and mixed-signal IC design engineers who wish to acquire practical knowledge of high-performance LDO circuits and a top-down understanding of advanced LDO topologies. The participants will explore a range of fully integrated LDOs, including analog, digital, and distributed architectures. Familiarity with fundamental LDO concepts will be beneficial.

All Lectures @ (23:00-01:00 Tokyo) = (16:00-18:00 Milan) = (15:00-17:00 Dublin) = (10:00-12:00 Boston) = (07:00-09:00 San Diego)

9th September 2025

Lecture #1 – Fundamentals of Low-Dropout Regulator (LDO)

LDO Applications and Specifications; Loop Bandwidth and Stability; Power Supply Rejection (PSR); PMOS or NMOS Power Transistor; Case Study.

11th September 2025

Lecture #2 – Analog LDO and Capacitor-less LDO Design

Gate-Drive Buffers; Adaptive and Dynamic Biasing; PSR Design Considerations; Capacitor-less LDOs; Case Study.

15th September 2025

Lecture #3 – LDO PSR Enhancement Techniques

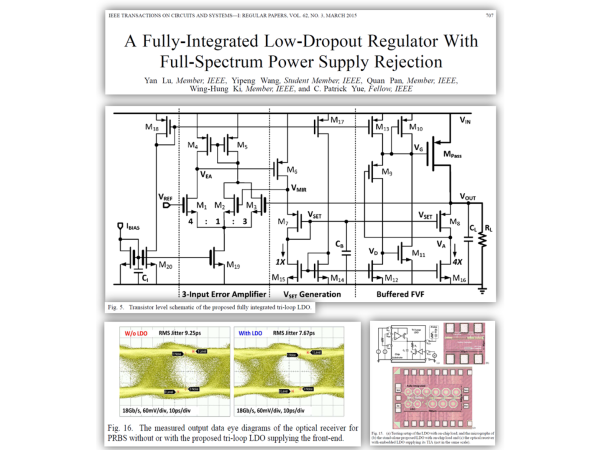

Feedforward Ripple Cancellation Techniques; Cascade LDOs; LDO with Cascode Power Transistors; Case Study.

18th September 2025

Lecture #4 – Digital LDO Design

Shift-Register-Based Digital LDO; Stability Analysis; Limit Cycle Oscillation; Digital LDO Examples; Case Study.

22nd September 2025

Lecture #5 – Distributed LDO on Large Chip

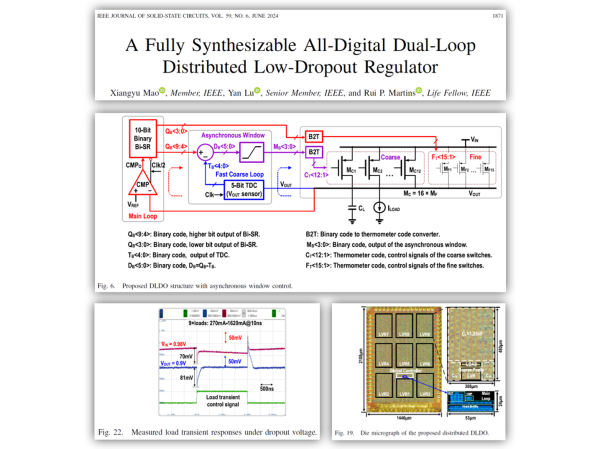

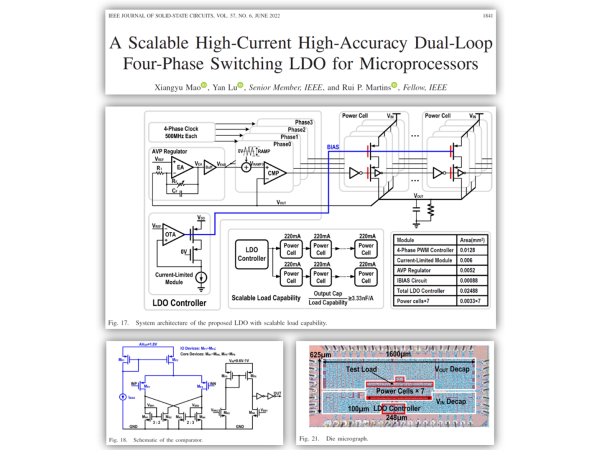

Switching LDO; Fully-Synthesizable Distributed Digital LDO; Case Study.

25th September 2025

Lecture #6 – PID Loop Analysis and Layout Design

PID Control in LDOs; Large Signal Techniques in LDOs; Layout for Power Circuits; Case Study.

29th September 2025

Lecture #7 – Design Project #1 – High-Bandwidth LDO

From-specs-to-sims; Step-by-step High-Bandwidth LDO Design and Simulation.

2nd October 2025

Lecture #8 – Design Project #2 – High-PSR LDO

From-specs-to-sims; Step-by-step High-PSR LDO Design and Simulation.

Duration: 16 hours

Format: 8 x 2-hour ‘Live-Virtual’ lectures (including Q&A), spread over 4-weeks. Attendance to the live lecture(s) is encouraged but not compulsory*.

Work: Homework assignments (optional) will consolidate the learning from the lectures.

Included:

- Course notes (PDF)

- Homework assignments (PDF)

- Lecture recordings* (up to 12 months playback access)

- Course homepage

- Class discussion forum (offline Q&A)

- Recommended reading list

- Extra material

- Attendance certificate

* Facilitates catch-up with a missed lecture(s) due to various reasons, e.g. time-zone difference, project deadline, travel, etc., or simply to review the lecture content at your own pace.

Yan Lu (Senior Member, IEEE) received the B.Eng. and M.Sc. degrees in microelectronic engineering from the South China University of Technology, Guangzhou, China, in 2006 and 2009, respectively, and the Ph.D. degree in electronic and computer engineering from the Hong Kong University of Science and Technology, Hong Kong, in 2013.

From 2014 to 2024, he was with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macau, China.

In 2024 he joined the Department of Electronic Engineering, Tsinghua University, Beijing, China, as a Full Professor with the Endowed Xing-Hua Chair Professorship. His research interests include high-density power converters, integrated voltage regulators, wireless power transfer and energy-harvesting circuits and systems. He has authored/co-authored 200+ peer-reviewed technical articles and three books, including 60+ ISSCC/JSSC papers and one newly published book “Fully-Integrated Low-Dropout Regulators” by Springer.

Dr. Lu has served as an ITPC Member (2020-2024) for ISSCC, as a TPC Member (2019-2022) and then the Power Management Subcommittee Chair (2023-2024) for CICC, an IEEE SSCS Distinguished Lecturer (2022–2023) and an IEEE CAS Society Distinguished Lecturer (2025–2026). He has served as a Guest Editor for the IEEE JSSC in 2022, 2023 and 2024, for the IEEE TCAS-I in 2019, and for the IEEE TCAS-II in 2018 and 2019. He has also served as a Young Editor (2021-2023) and is the Associate Editor (Direction-2: IC Design and Applications) for the Journal of Semiconductors since 2024. He was a recipient/corecipient of the IEEE Solid-State Circuits Society Pre-Doctoral Achievement Award (2013–2014), the IEEE CAS Society Outstanding Young Author Award in 2017, and the ISSCC 2017 Takuo Sugano Award for Outstanding Far-East Paper.

Patents & Publications

LDO Patents (Selected)

Limit cycle oscillation reduction for digital low dropout regulators

LDO Publications (Selected)

[2025] Fully-Integrated Low-Dropout Regulators

[2024] A Fully Synthesizable All-Digital Dual-Loop Distributed Low-Dropout Regulator

[2023] A High-Current Scalable Parallel LDO Scheme With Analog-Digital Merged Control for Small Current-Sharing Mismatch

[2022] A Scalable High-Current High-Accuracy Dual-Loop Four-Phase Switching LDO for Microprocessors

[2021] A Fully Integrated FVF LDO With Enhanced Full-Spectrum Power Supply Rejection

[2020] An NMOS Digital LDO With NAND-Based Analog-Assisted Loop in 28nm CMOS

[2020] A Fully Integrated LDO With 50mV Dropout for Power Efficiency Optimization

[2020] An Analog-Proportional Digital-Integral Multiloop Digital LDO With PSR Improvement and LCO Reduction

[2018] An Analog-Assisted Tri-Loop Digital Low-Dropout Regulator

[2016] An NMOS-LDO Regulated Switched-Capacitor DC–DC Converter With Fast-Response Adaptive-Phase Digital Control

[2016] A 312ps response-time LDO with enhanced super source follower in 28nm CMOS

[2015] A Fully-Integrated Low-Dropout Regulator With Full-Spectrum Power Supply Rejection

Course Report