“ICONS 2026: Masterclass Series on Advanced IC Design” Online Course

Interview with Prof. Boris Murmann (University of Hawai’i)

Preview – Lecture #1

Preview – Lecture #2

Preview – Lecture #3

Preview – Lecture #4

Preview – Lecture #5

With data rates pushing beyond 200Gbps and ADC resolution being impacted by a single picosecond of jitter, the boundaries between signal precision, timing integrity and high-speed connectivity are disappearing.

The ICONS 2026 Masterclass Series addresses this convergence through deep-dive sessions into high-performance circuit design. Covering Data Conversion, Frequency Synthesis, and Wireline Transceivers, each session establishes the fundamental “why” followed by the practical “how” of implementation.

State-of-the-art digital-friendly solutions, including Time-Domain ADCs, Dynamic Residue Amplifiers, and Hybrid PLLs, are presented. The series concludes with an extraordinary talk beyond conventional circuit schematics, exposing participants to the challenges of advanced Metrology.

Optional hands-on assignments, ranging from SPICE-based verification of circuit performance to analytical problems and system-level modelling, provide the participants the opportunity to consolidate the learning beyond the lecture material.

The course is primarily aimed at analog and mixed-signal IC design engineers with existing exposure to ADCs, PLLs and SerDes design. The programme will empower participants to transcend standard design methodologies to deliver production-ready solutions.

The masterclass series is organised into eight focused sessions:

Lecture #1 – Systematic Design of Sampling Circuits (Boris Murmann – University of Hawai’i)

Lecture #2 – Advanced Residue Amplifier Design for Pipelined ADCs (Seung-Tak Ryu – KAIST)

Lecture #3 – Time-Domain ADCs: From Fundamentals to Silicon-Ready Design (Chi-Hang Chan – University of Macau)

Lecture #4 – Hybrid PLLs with Linear Phase Detection (Woogeun Rhee – Sungkyunkwan University)

Lecture #5 – CTLE Design Methodology for High-Speed Wireline Systems (Gain Kim – DGIST)

Lecture #6 – System and Circuit Modeling for Modern SerDes Links (Kevin Zheng – AMD/Xilinx)

Lecture #7 – Harmonic LC Oscillators: Fundamental Limits and Design Trade-Offs (Antonio Liscidini -University of Toronto)

Lecture #8 – From DC to Light – Measurement Techniques & Pitfalls (Shahriar Shahramian – Nokia Bell Labs)

* Lecture Time (22:00-00:00 Tokyo) = (15:00-17:00 Milan) = (14:00-16:00 Dublin) = (09:00-11:00 Toronto) = (06:00-08:00 San Jose)

** Lecture Time (01:00-03:00 Tokyo) = (18:00-20:00 Milan) = (17:00-19:00 Dublin) = (12:00-14:00 Toronto) = (09:00-11:00 San Jose)

Week #1 – Tuesday, 5th May 2026 **

Lecture #1 – Systematic Design of Sampling Circuits

Presenter: Boris Murmann (University of Hawai’i)

Abstract: Sampling circuits are essential ingredients of a wide variety of signal chains in high-performance integrated circuits. While their basic design trade-offs and asymptotic performance limits are relatively well understood, there is limited material on dissecting the design flow and careabouts for practical applications.

This presentation will build on two illustrative examples, one tailored toward ultra-high speed and one for ultra-low distortion, to derive and illustrate practical design approaches. In addition to delivering end-to-end CMOS designs from specs to device sizes, it will review important underpinnings such as kT/C noise, jitter, tracking nonlinearities, charge injection, as well as circuit simulation techniques.

Week #1 – Thursday, 7th May 2026 *

Lecture #2 – Advanced Residue Amplifier Design for Pipelined ADCs

Presenter: Seung-Tak Ryu (KAIST)

Abstract: Residue amplifier is the most important building block in a pipelined ADC that determines the linearity, speed, and power efficiency. Achieving sufficient bandwidth and DC gain is constrained by limited power budgets and reduced supply voltages in modern CMOS processes. To satisfy given design challenges, it is necessary to know how to derive amplifier specifications from system-level targets and to know how to design amplifiers to meet the specifications.

This session presents design methodologies for residue amplifiers, beginning with the derivation of circuit parameters such as open-loop gain and bandwidth from ADC system specifications. The technical content first reviews a traditional op-amp based design with a focus on maintaining feedback stability and precision. Then, it goes through closed-loop residue amplifier design with dynamic amplifiers using ring amplifier (Ringamp) and/or floating inverter amplifiers (FIA) which offer improved power scalability. The session also discusses design considerations for PVT-robustness of the dynamic behaviours.

Week #2 – Monday, 11th May 2026 *

Lecture #3 – Time-Domain ADCs: From Fundamentals to Silicon-Ready Design

Presenter: Chi-Hang Chan (University of Macau)

Abstract: Time-domain (TD) analog-to-digital converters (ADCs) are emerging solutions for high-speed data acquisition systems, as well as sub-ADCs for massive time-interleaving ADCs, offering unique advantages in power scalability, digital compatibility, and process portability. Despite significant advances in recent years, learning materials that fundamentally explain the underlying theory, the complete design flow, practical decision-making, and the subtle considerations required for real-world implementation remain absent.

This lecture begins by establishing the foundational concepts of TD ADCs. It then provides an overview of various voltage-to-time converter (VTC) topologies and TD ADC architectures. Finally, a moderate‑resolution, high-speed flash-based TD ADC design example is presented. Through this example, the session covers practical design strategies—from interpreting given specifications to achieving transistor-level realization—and highlights key design considerations for critical building blocks, including VTC nonlinearity, zero-crossing detectors, delay lines, and TD comparators. Along the way, it also discusses essential simulation and verification techniques to ensure process voltage and temperature (PVT) robust implementations from concept to silicon-ready designs.

Week #2 – Thursday, 14th May 2026 *

Lecture #4 – Hybrid PLLs with Linear Phase Detection

Presenter: Woogeun Rhee (Sungkyunkwan University)

Abstract: While removing the analog loop filter is considered an innovative solution in recent PLL works, the all-digital PLL (ADPLL) requires a high-resolution time-to-digital converter (TDC) or a digital-to-time converter (DTC), which significantly increases design complexity over PVT variations. To achieve a leakage-current-insensitive and technology-scalable architecture comparable to that of ADPLLs, a hybrid (HPLL) with linear phase detection can be considered as an alternative.

In this talk, a brief review of the HPLL in comparison with the ADPLL will be presented. Then, two specific design examples for low-voltage clock generation and frequency modulation based on charge-pump-less HPLL architectures will be discussed. Voltage-domain quantization noise reduction techniques will also be covered.

Week #3 – Monday, 18th May 2026 *

Lecture #5 – CTLE Design Methodology for High-Speed Wireline Systems

Presenter: Gain Kim (DGIST)

Abstract: In high-speed SerDes systems, the continuous-time linear equalizer (CTLE) is a critical analog front-end component that compensates for frequency-dependent channel loss within tight power and area budgets. As data rates increase and PAM modulation orders rise, meeting requirements for bandwidth, peaking gain, and linearity becomes increasingly challenging.

This session explains why the CTLE remains essential for modern wireline receivers and discusses the trade-offs involved in its design. It also provides a step-by-step methodology for designing a CTLE, moving from initial specifications to transistor sizing and the determination of passive element values with a practical design example for a high-speed PAM-4 receiver.

Week #3 – Thursday, 21st May 2026 *

Lecture #6 – System and Circuit Modeling for Modern SerDes Links

Presenter: Kevin Zheng (AMD/Xilinx)

Abstract: High-performance SerDes is one of the work horses that’s enabling key technological advancements in the age of AI. Good modeling and analysis methodologies for a complex SerDes system are increasingly important to serve as the beacon to guide circuit, algorithm and system designs.

This talk will cover basic signal processing concepts in a modern SerDes link (equalization, CDR), key circuit impairments that need to be modeled (including jitter, noise, etc.), and different analysis methods (statistical vs. transient simulations). There will also be a brief discussion on software mentality for hardware engineers.

Week #4 – Monday, 25th May 2026 *

Lecture #7 – Harmonic LC Oscillators: Fundamental Limits and Design Trade-Offs

Presenter: Antonio Liscidini (University of Toronto)

Abstract: Harmonic LC oscillators are critical components in high-speed and high-precision integrated circuits, where they enable low-jitter clocking and frequency generation for applications such as data converters, wireline links, and wireless transceivers. In these systems, oscillator performance directly limits achievable resolution, timing accuracy, and spectral purity. As a result, design choices are often constrained not only by implementation details but by fundamental limits on phase noise, power efficiency, and tunability imposed by resonator losses, device noise, and nonlinear operation.

This presentation highlights these fundamental limitations and develops a systematic design framework for harmonic LC oscillators. It examines how power efficiency, operating class, phase-noise performance, tuning trade-offs evolve across different oscillator topologies. Practical considerations such as tank tunability, varactor nonlinearity and flicker noise up-conversion, and the impact of active-device noise are discussed in the context of realistic CMOS implementations. Using analytical models and illustrative design examples, the talk connects system-level specifications to circuit-level choices and simulation techniques, providing a clear view of the performance boundaries faced in modern LC oscillator design.

Week #4 – Thursday, 28th May 2026 *

Lecture #8 – From DC to Light – Measurement Techniques & Pitfalls

Presenter: Shahriar Shahramian (Nokia Bell Labs)

Abstract: Despite the central role of instrumentation in electrical engineering, metrology techniques, and their common pitfalls, are often underemphasized in university curricula. Inaccurate measurements can undermine a researcher’s credibility and lead to costly setbacks, potentially amounting to millions of dollars during product development and commercialization. At the same time, instrumentation technologies have advanced rapidly, blurring the boundaries between measurement domains. This progress, however, has introduced new challenges: increasing complexity in measurement setups, abstraction of instrument functions, and limited user experience frequently contribute to misleading or erroneous characterizations.

This tutorial explores frequency-, time-, and mixed-domain measurements, with particular emphasis on noise figure, phase noise, broadband modulation, sub-THz signal detection, eye-diagram capture, and frequency conversion behavior. These topics will be examined through the lens of diverse instrumentation architectures that enable such measurements. Additionally, we will highlight the precision, accuracy, repeatability, and resolution limits of various instruments to underscore the importance of uncertainty quantification, error bars, and robust fault detection.

Duration: 16 hours

Format: 8 x 2-hour ‘Live-Virtual’ lectures (including Q&A), spread over 4-weeks. Attendance to the live lecture(s) is encouraged but not compulsory*.

Work: Homework assignments (optional) will consolidate the learning from the lectures.

Included:

- Course notes (PDF)

- Homework assignments (PDF)

- Lecture recordings* (up to 12 months playback access)

- Course homepage

- Class discussion forum (offline Q&A)

- Recommended reading list

- Extra material

- Attendance certificate

* Facilitates catch-up with a missed lecture(s) due to various reasons, e.g. time-zone difference, project deadline, travel, etc., or simply to review the lecture content at your own pace.

Boris Murmann

University of Hawai’i

Seung-Tak Ryu

KAIST

Chi-Hang Chan

University of Macau

Woogeun Rhee

Sungkyunkwan University

Gain Kim

DGIST

Kevin Zheng

AMD/Xilinx

Antonio Liscidini

University of Toronto

Shahriar Shahramian

Bell Laboratories, Nokia

Publications (Selected)

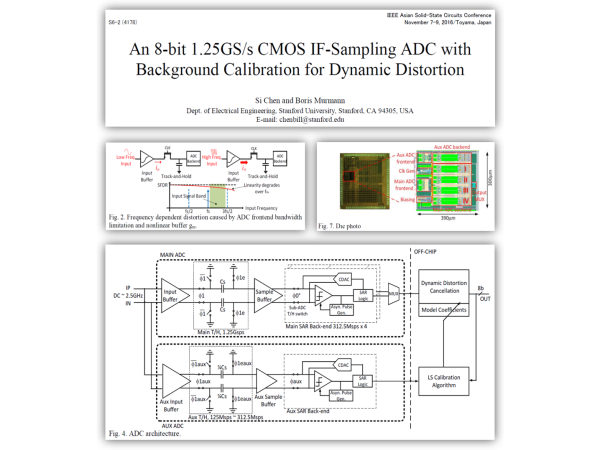

[2016] An 8-bit 1.25GS/s CMOS IF-sampling ADC with background calibration for dynamic distortion

[2012] Thermal Noise in Track-and-Hold Circuits: Analysis and Simulation Techniques

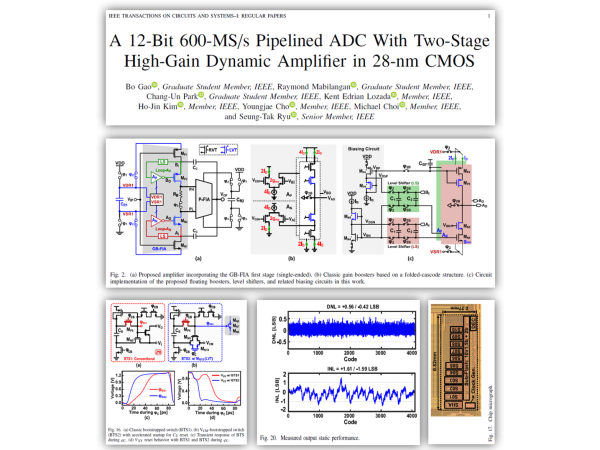

[2025] A 12-Bit 600-MS/s Pipelined ADC With Two-Stage High-Gain Dynamic Amplifier in 28-nm CMOS

[2025] A 10b 3GS/s Time-Domain ADC with Mutually Exclusive Metastability Correction and Wide Common-Mode Input

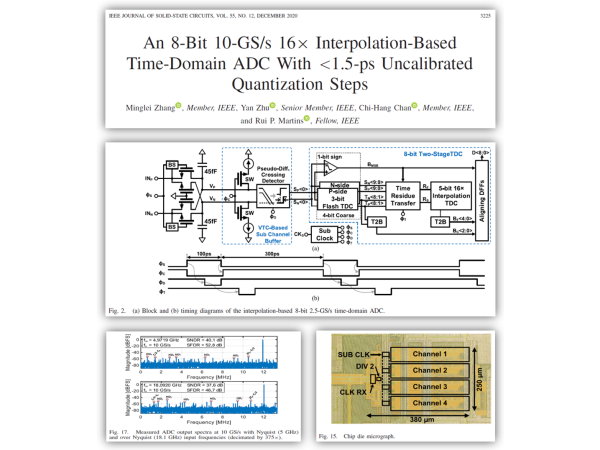

[2020] An 8-Bit 10-GS/s 16× Interpolation-Based Time-Domain ADC With <1.5-ps Uncalibrated Quantization Steps

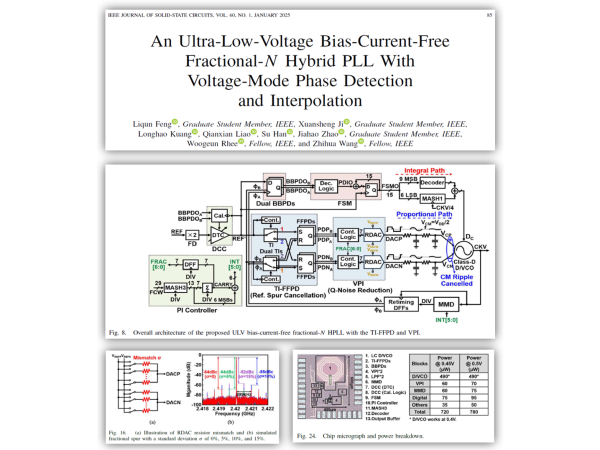

[2025] An Ultra-Low-Voltage Bias-Current-Free Fractional-N Hybrid PLL With Voltage-Mode Phase Detection and Interpolation

[2024] A 0.6V Fully-Integrated BLE Transmitter in 65nm CMOS Using a Common-Mode-Ripple-Cancelled Hybrid PLL …

[2018] System-driven circuit design for ADC-based wireline data links

[2014] An Intuitive Analysis of Phase Noise Fundamental Limits Suitable for Benchmarking LC Oscillators

[2014] A Power-Scalable DCO for Multi-Standard GSM/WCDMA Frequency Synthesizers

[2010] Capacitive Degeneration in LC-Tank Oscillator for DCO Fine-Frequency Tuning